DS18B20 온도 센서 지식 소개

DS18B20은 일반적으로 사용되는 디지털 온도 센서입니다.. 디지털 신호를 출력합니다., 작은 크기의 특징을 가지고 있습니다, 낮은 하드웨어 오버헤드, 강력한 간섭 방지 능력, 높은 정밀도, 그리고 널리 사용된다.

DS18B20 온도 센서 소개

기술적 특징:

①. 고유한 단일 와이어 인터페이스 모드. DS18B20이 마이크로프로세서에 연결된 경우, 오직 1 마이크로프로세서와 DS18B20 간의 양방향 통신을 실현하려면 와이어가 필요합니다..

②. 온도 측정 범위 -55 ℃~+125 ℃, 고유온도 측정오차 1℃.

③. 멀티 포인트 네트워킹 기능을 지원합니다. 단 3개의 전선으로 여러 개의 DS18B20을 병렬로 연결할 수 있습니다., 그리고 최대 8 다중 지점 온도 측정을 실현하기 위해 병렬로 연결할 수 있습니다.. 숫자가 너무 큰 경우, 전원 공급 장치 전압이 너무 낮습니다, 불안정한 신호 전송이 발생합니다.

④. 작업 전원 공급 장치: 3.0~ 5.5V/DC (데이터 라인 기생충 전원 공급 장치를 사용할 수 있습니다).

⑤. 사용 중에는 주변 구성 요소가 필요하지 않습니다..

⑥. 측정 결과는 9~12비트 디지털 형식으로 직렬로 전송됩니다..

⑦. 스테인레스 스틸 보호 튜브의 직경은 Φ6입니다..

⑧. DN15~25의 다양한 중공업 파이프라인의 온도 측정에 적합합니다., DN40~DN250 및 좁은 공간의 장비.

⑨. 표준 설치 스레드 M10X1, M12x1.5, G1/2”는 선택 사항입니다..

⑩. PVC 케이블을 직접 연결하거나 독일산 볼형 정션박스를 연결하는 경우, 다른 전기 장비와의 연결에 편리합니다..

DS18B20 읽기 및 쓰기 타이밍 및 온도 측정 원리:

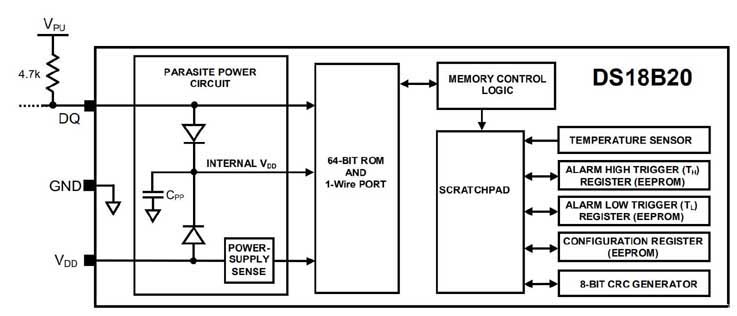

DS18B20 온도 측정 원리는 그림에 나와 있습니다. 1. 그림의 저온 계수 수정 발진기의 발진 주파수는 온도의 영향을 거의 받지 않습니다., 카운터로 전송 될 고정 주파수 펄스 신호를 생성하는 데 사용됩니다. 1. 고온 계수 수정 발진기의 발진 주파수는 온도에 따라 크게 변합니다., 생성된 신호는 카운터의 펄스 입력으로 사용됩니다. 2. 계수기 1 온도 레지스터는 -55℃에 해당하는 기본 값으로 사전 설정되어 있습니다.. 계수기 1 저온 계수 수정 발진기에서 생성된 펄스 신호를 뺍니다.. 카운터의 사전 설정 값 1 로 감소된다 0, 온도 레지스터의 값은 1, 그리고 카운터의 사전 설정 1 다시로드됩니다. 계수기 1 저온 계수 수정 발진기에 의해 생성된 펄스 신호를 계산하기 위해 다시 시작됩니다., 사이클은 카운터까지 계속됩니다. 2 카운트 0, 온도 레지스터 값의 축적 중지. 이때, 온도 레지스터의 값은 측정 된 온도입니다.. 경사 축적기는 온도 측정 과정에서 비선형 성을 보상하고 수정하는 데 사용됩니다., 그리고 출력은 카운터의 사전 설정 값을 수정하는 데 사용됩니다. 1.

수치 1 다음과 같습니다:

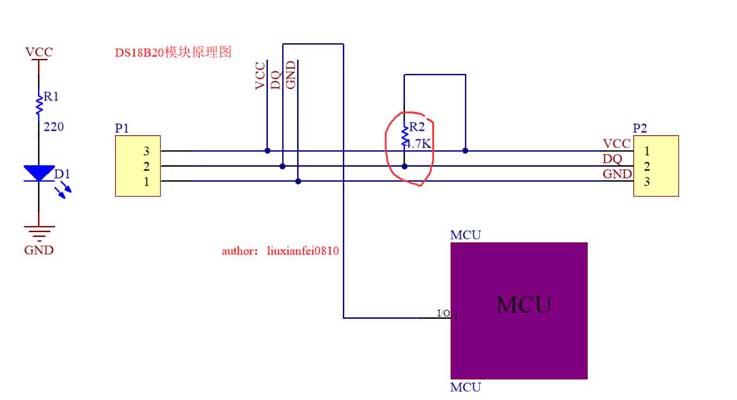

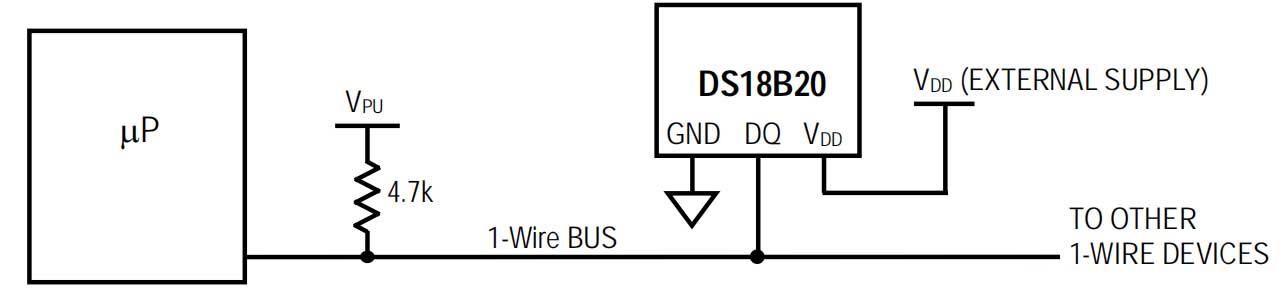

2. DS18B20 및 MCU 연결 다이어그램

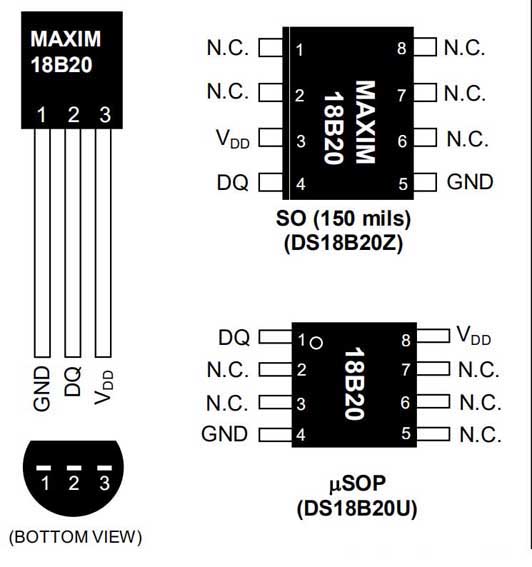

3. DS18B20 핀 정의:

DQ: 데이터 입출력. 오픈 드레인 1선 인터페이스. 또한 기생 전력 모드 VDD에서 사용될 때 장치에 전력을 공급할 수도 있습니다.: 양극 전원 GND: 전원 접지 4. DS18B20 내부 분석 소개:

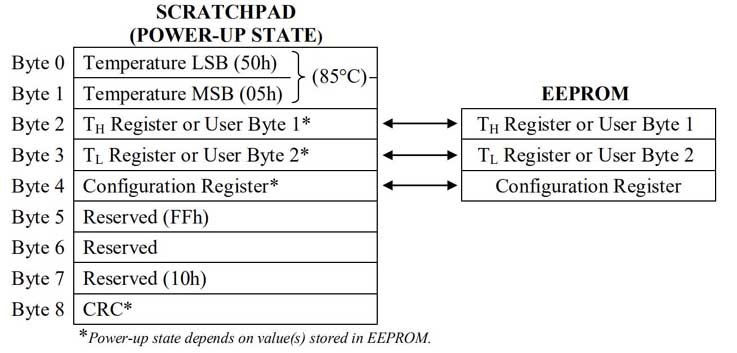

위 그림은 DS18B20의 블록 다이어그램을 보여줍니다., 64비트 ROM에는 장치의 고유한 직렬 코드가 저장됩니다.. 버퍼 메모리에는 2 온도 센서의 디지털 출력을 저장하는 온도 레지스터 바이트. 게다가, 버퍼 메모리는 1바이트 상위 및 하위 경보 트리거 레지스터에 대한 액세스를 제공합니다. (TH와 TL) 및 1바이트 구성 레지스터. 구성 레지스터를 사용하면 온도 분해능을 디지털 변환으로 설정할 수 있습니다. 9, 10, 11, 또는 12 비트. 일, TL, 구성 레지스터는 비휘발성입니다. (EEPROM), 그래서 장치의 전원이 꺼져도 데이터가 유지됩니다.. DS18B20은 Maxim의 고유한 1선 버스 프로토콜을 사용합니다., 제어 신호를 사용하는 것. 모든 장치가 3상 또는 오픈 드레인 포트를 통해 버스에 연결되므로 제어 라인에는 약한 풀업 저항이 필요합니다. (DS18B20의 경우 DQ 핀). 이 버스 시스템에서는 마이크로프로세서 (주인) 각 장치마다 고유한 64비트 코드를 사용합니다.. 기기마다 고유한 코드가 있기 때문에, 하나의 버스에서 처리할 수 있는 장치 수는 사실상 무제한입니다..

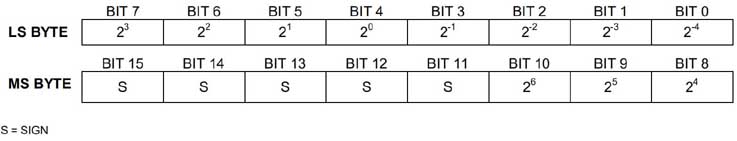

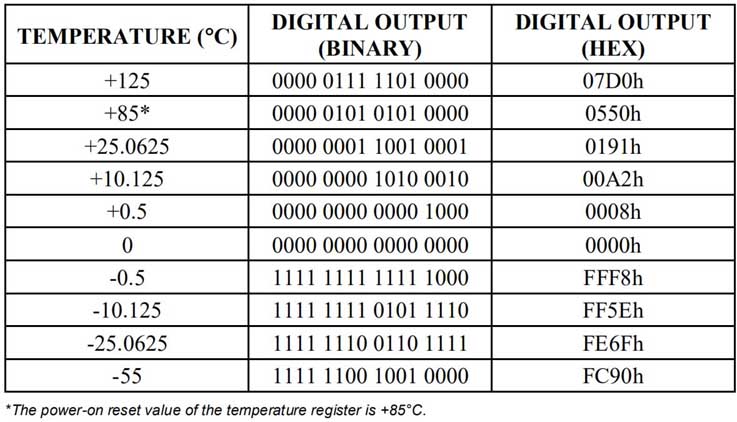

온도 레지스터 형식

온도/데이터 관계

작동 경보 신호

DS18B20이 온도 변환을 수행한 후, 온도 값을 1바이트 TH 및 TL 레지스터에 저장된 사용자 정의 2의 보수 경보 트리거 값과 비교합니다.. 부호 비트는 값이 양수인지 음수인지를 나타냅니다.: 양의 S=0, 음수 S=1. TH 및 TL 레지스터는 비휘발성입니다. (EEPROM) 따라서 장치의 전원이 꺼져도 휘발성이 아닙니다.. TH와 TL은 바이트를 통해 액세스할 수 있습니다. 2 그리고 3 기억의.

TH 및 TL 레지스터 형식:

외부 전원 공급 장치를 사용하여 DS18B20에 전원을 공급하는 회로도

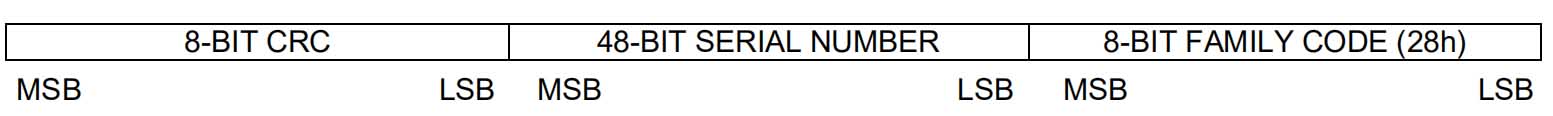

64-비트 레이저 읽기 전용 메모리 코드:

각 DS18B20에는 ROM에 저장된 고유한 64비트 코드가 포함되어 있습니다.. 가장 중요하지 않은 8 ROM 코드의 비트에는 DS18B20의 단일 와이어 제품군 코드가 포함되어 있습니다.: 28시간. 다음 48 비트에는 고유한 일련 번호가 포함되어 있습니다.. 가장 중요한 8 비트에는 순환 중복 검사가 포함되어 있습니다. (CRC) 바이트, 처음부터 계산된 것입니다. 56 ROM 코드의 비트.

DS18B20 메모리 맵

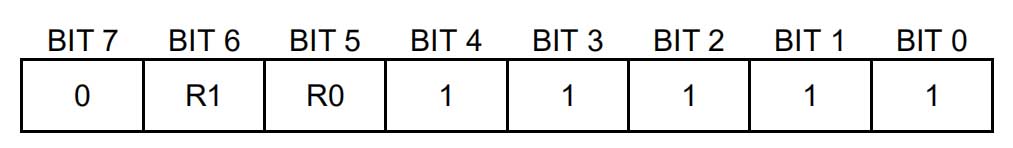

구성 레지스터:

수치 2

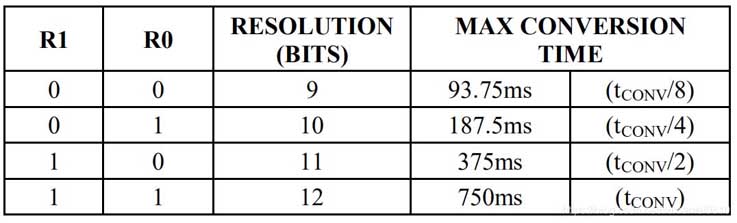

바이트 4 메모리에는 구성 레지스터가 포함되어 있습니다., 그림과 같이 구성되어 있습니다 2. 사용자는 표에 표시된 대로 비트 R0 및 R1을 사용하여 DS18B20의 변환 해상도를 설정할 수 있습니다. 2. 이러한 비트의 전원 켜기 기본값은 R0 = 1 그리고 R1 = 1 (12-비트 해상도). 해결과 전환 시간 사이에는 직접적인 관계가 있습니다.. 조금 7 그리고 비트 0 에게 4 구성 레지스터의 내용은 장치 내부용으로 예약되어 있으므로 덮어쓸 수 없습니다..

테이블 2 온도계 분해능 구성

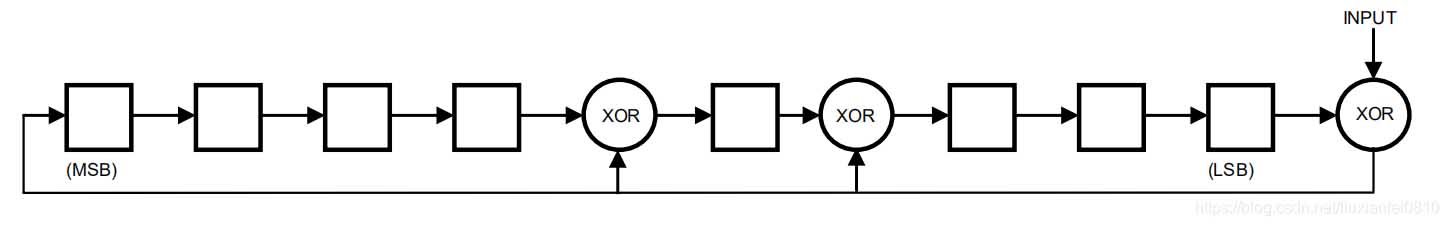

CRC 생성

CRC 바이트는 DS18B20 64비트 ROM 코드의 일부이며 스크래치패드의 9번째 바이트에 제공됩니다.. ROM 코드 CRC는 첫 번째부터 계산됩니다. 56 ROM 코드의 비트이며 ROM의 최상위 바이트에 포함되어 있습니다.. 스크래치패드 CRC는 스크래치패드에 저장된 데이터를 기반으로 계산됩니다., 스크래치 패드의 데이터가 변경되면 변경됩니다.. CRC는 DS18B20에서 데이터를 읽을 때 버스 호스트에 데이터 확인 방법을 제공합니다.. 데이터가 올바르게 읽혀졌는지 확인한 후, 버스 마스터는 수신된 데이터에서 CRC를 다시 계산한 다음 해당 값을 ROM 코드 CRC와 비교해야 합니다. (ROM 읽기의 경우) 또는 스크래치패드 CRC (스크래치패드 읽기용). 계산된 CRC가 읽은 CRC와 일치하는 경우, 데이터가 올바르게 수신되었습니다. CRC 값을 비교하고 진행하는 결정은 전적으로 버스 마스터의 재량입니다.. DS18B20 내부에는 다음과 같은 경우 명령 시퀀스 실행을 방지하는 회로가 없습니다.:

DS18B20 CRC (ROM 또는 스크래치패드) 버스 마스터에서 생성된 값과 일치하지 않습니다..

CRC에 대한 등가 다항식 함수는 다음과 같습니다.:

CRC = X8 + X5 + X4 + 1

버스 마스터는 CRC를 다시 계산하고 이를 DS18B20의 CRC 값과 비교할 수 있습니다.:

다항식 생성기는 그림에 나와 있습니다. 3. 회로에는 시프트 레지스터와 yihuo 게이트가 포함되어 있습니다., 시프트 레지스터의 비트는 다음과 같이 초기화됩니다. 0. ROM 코드의 최하위 비트 또는 바이트의 최하위 비트 0 스크래치패드에서 한 번에 하나씩 시프트 레지스터로 이동되어야 합니다.. 비트 단위로 이동한 후 56 ROM 또는 가장 중요한 바이트 비트에서 7 스크래치패드에서, 다항식 생성기는 다시 계산된 CRC를 포함합니다.. 다음, 스크래치패드 DS18B20의 8비트 ROM 코드 또는 CRC 신호는 회로로 이동되어야 합니다.. 이 시점에서, 다시 계산된 CRC가 올바른 경우, 시프트 레지스터는 모두 0이 됩니다..

수치 3: CRC 생성기

V. DS18B20에 액세스:

DS18B20에 접속하는 순서는 다음과 같습니다:

단계 1. 초기화;

단계 2. ROM 명령 (필요한 데이터 교환이 이어집니다.);

단계 3. DS18B20 기능 명령 (필요한 데이터 교환이 이어집니다.);

메모: DS18B20에 액세스할 때마다 이 순서를 따릅니다., 시퀀스의 단계 중 하나라도 누락되거나 순서가 잘못된 경우 DS18B20이 응답하지 않기 때문입니다.. 이 규칙의 예외는 검색 ROM입니다. [F0h] 및 알람 검색 [에흐] 명령. 이 두 개의 ROM 명령을 실행한 후, 호스트는 단계로 돌아가야 합니다 1 순서대로.

(위 소개는 공식 매뉴얼을 번역한 것입니다.)

ROM 명령

1, ROM을 읽으십시오 [33시간]

2, 일치 ROM [55시간]

3, 배 [CCh]

4, 알람 검색 [에흐]

DS18B20 기능 명령

1, 온도 변환 [44시간]

2, 스크래치 패드를 작성하십시오 (메모리) [4뭐라고]

3, 스크래치 패드를 읽습니다 (메모리) [베]

4, 스크래치 패드를 복사하십시오 (메모리 [48시간]

5, E2 다시 깨우기 [B8h]

6, 읽기 전력 [B4h]

(위의 명령에 대한 자세한 설명은, 공식 매뉴얼을 참조하세요)

VI. DS18B20 타이밍에 액세스

초기화 과정 중, 버스 마스터가 재설정 펄스를 보냅니다. (텍사스) 1-Wire 버스를 당겨 최소 480μs 동안 로우 레벨 유지. 그 다음에, 버스 마스터는 버스를 해제하고 수신 모드로 들어갑니다. (RX). 버스를 내린 후, 5kΩ 풀업 저항은 1-Wire 버스를 하이로 끌어옵니다.. DS18B20이 이 상승 에지를 감지하면, 15~60μs 동안 기다린 후 60~240μs 동안 1-Wire 버스를 로우로 당겨 존재 펄스를 보냅니다..

초기화 타이밍:

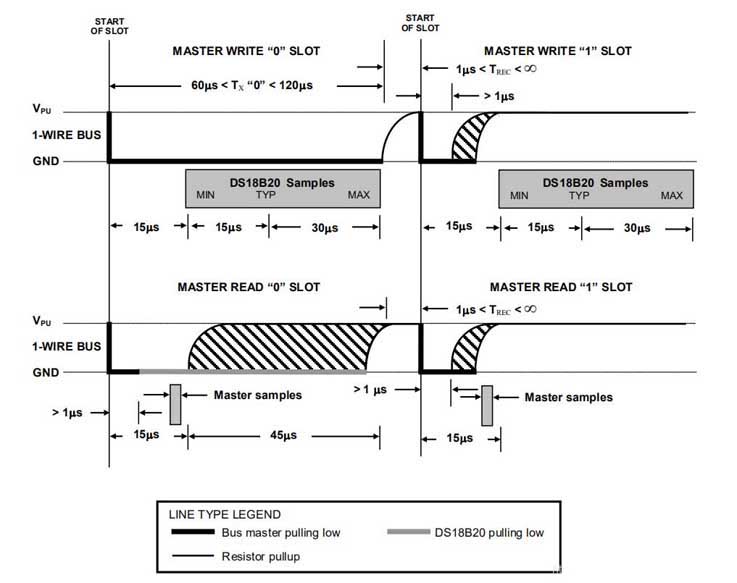

쓰기 시간 슬롯에는 두 가지 유형이 있습니다.: “1개를 쓰세요” 시간 슬롯과 “0을 쓰세요” 시간 슬롯. 버스는 쓰기를 사용합니다 1 로직을 작성하는 시간 1 DS18B20 및 쓰기 0 로직을 작성하는 시간 0 DS18B20에. 모든 쓰기 시간 슬롯은 지속 시간이 최소 60μs여야 하며 개별 쓰기 시간 슬롯 사이의 복구 시간은 최소 1μs여야 합니다.. 두 가지 유형의 쓰기 타임 슬롯 모두 마스터가 1-Wire 버스를 로우로 끌어당김으로써 시작됩니다. (그림 참조 14). 쓰기를 생성하려면 1 시간대, 1-Wire 버스를 로우로 풀링한 후, 버스 마스터는 15μs 이내에 1-Wire 버스를 해제해야 합니다.. 버스를 내린 후, 5kΩ 풀업 저항은 버스를 높게 끌어옵니다.. 생성

쓰다 0 시간대, 1-Wire 라인을 로우로 당긴 후, 버스 마스터는 해당 시간 동안 버스를 계속해서 낮게 유지해야 합니다. (최소 60μs). DS18B20은 마스터가 쓰기 시간 슬롯을 시작한 후 15~60μs 범위 내에서 1-Wire 버스를 샘플링합니다.. 샘플링 기간 동안 버스가 높은 경우, 에이 1 DS18B20에 기록됩니다.. 라인이 낮으면, 에이 0 DS18B20에 기록됩니다..

메모: 타임슬롯은 단일 채널에 전용된 타임슬롯 정보의 직렬 자체 다중화의 일부입니다..

수치 14 다음과 같습니다:

시간 슬롯 읽기:

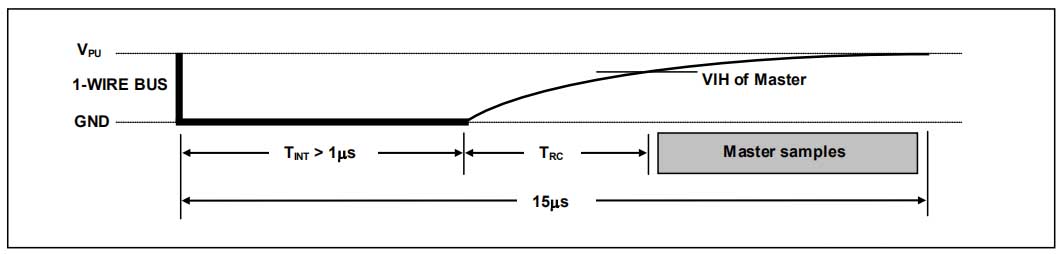

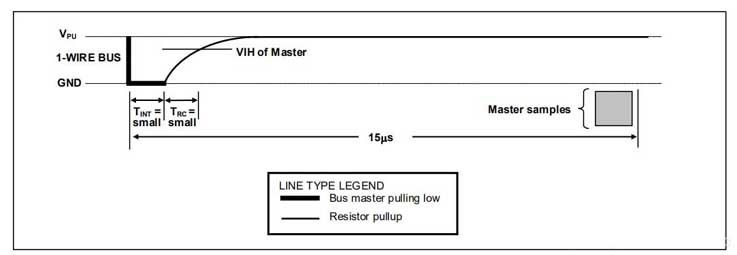

DS18B20은 호스트가 읽기 시간 슬롯을 발행할 때만 호스트에 데이터를 보낼 수 있습니다.. 그러므로, 호스트는 메모리 읽기 명령을 내린 후 즉시 읽기 시간 슬롯을 생성해야 합니다. [베] 또는 읽기 전원 공급 장치 [B4h] DS18B20이 필요한 데이터를 제공하기 위한 명령. 또는, 호스트는 Convert T를 발행한 후 읽기 시간 슬롯을 생성할 수 있습니다. [44시간] 또는 E2를 회상하세요. [B8h] 상태를 알아내는 명령. 모든 읽기 시간 슬롯은 지속 시간이 최소 60μs여야 하며 시간 슬롯 간 최소 복구 시간은 1μs여야 합니다.. 읽기 타임 슬롯은 마스터가 1-Wire 버스를 로우로 당겨 최소 1μs 동안 로우를 유지한 후 버스를 해제함으로써 시작됩니다. (그림 참조 14). 마스터가 읽기 시간 슬롯을 시작한 후, DS18B20은 버스에서 1 또는 0을 보내기 시작합니다.. DS18B20은 다음을 보냅니다. 1 버스를 높이 들고 다음을 보냅니다. 0 버스를 낮게 당겨서. 언제 0 전송됩니다, DS18B20은 버스를 높게 유지하여 버스를 해제합니다.. 타임 슬롯이 종료되고 버스는 풀업 저항에 의해 고속 유휴 상태로 되돌아갑니다..

English

English Afrikaans

Afrikaans العربية

العربية বাংলা

বাংলা bosanski jezik

bosanski jezik Български

Български Català

Català 粤语

粤语 中文(简体)

中文(简体) 中文(漢字)

中文(漢字) Hrvatski

Hrvatski Čeština

Čeština Nederlands

Nederlands Eesti keel

Eesti keel Suomi

Suomi Français

Français Deutsch

Deutsch Ελληνικά

Ελληνικά हिन्दी; हिंदी

हिन्दी; हिंदी Magyar

Magyar Bahasa Indonesia

Bahasa Indonesia Italiano

Italiano 日本語

日本語 한국어

한국어 Latviešu valoda

Latviešu valoda Lietuvių kalba

Lietuvių kalba македонски јазик

македонски јазик Bahasa Melayu

Bahasa Melayu Norsk

Norsk پارسی

پارسی Polski

Polski Português

Português Română

Română Русский

Русский Cрпски језик

Cрпски језик Slovenčina

Slovenčina Slovenščina

Slovenščina Español

Español Svenska

Svenska ภาษาไทย

ภาษาไทย Türkçe

Türkçe Українська

Українська اردو

اردو Tiếng Việt

Tiếng Việt